资料目录(截图原因可能偏模糊,实际都是高清版)

备考《数字电路》,最致命的误区是把它当成“电路分析”的延续去死磕电压电流,或者当成“文科”去死记真值表。这门课的本质是研究数字信号的逻辑关系和处理方法,核心是“逻辑”而非“电路”。从开关代数到复杂的时序系统,你是在学习如何用硬件语言描述和解决逻辑问题。

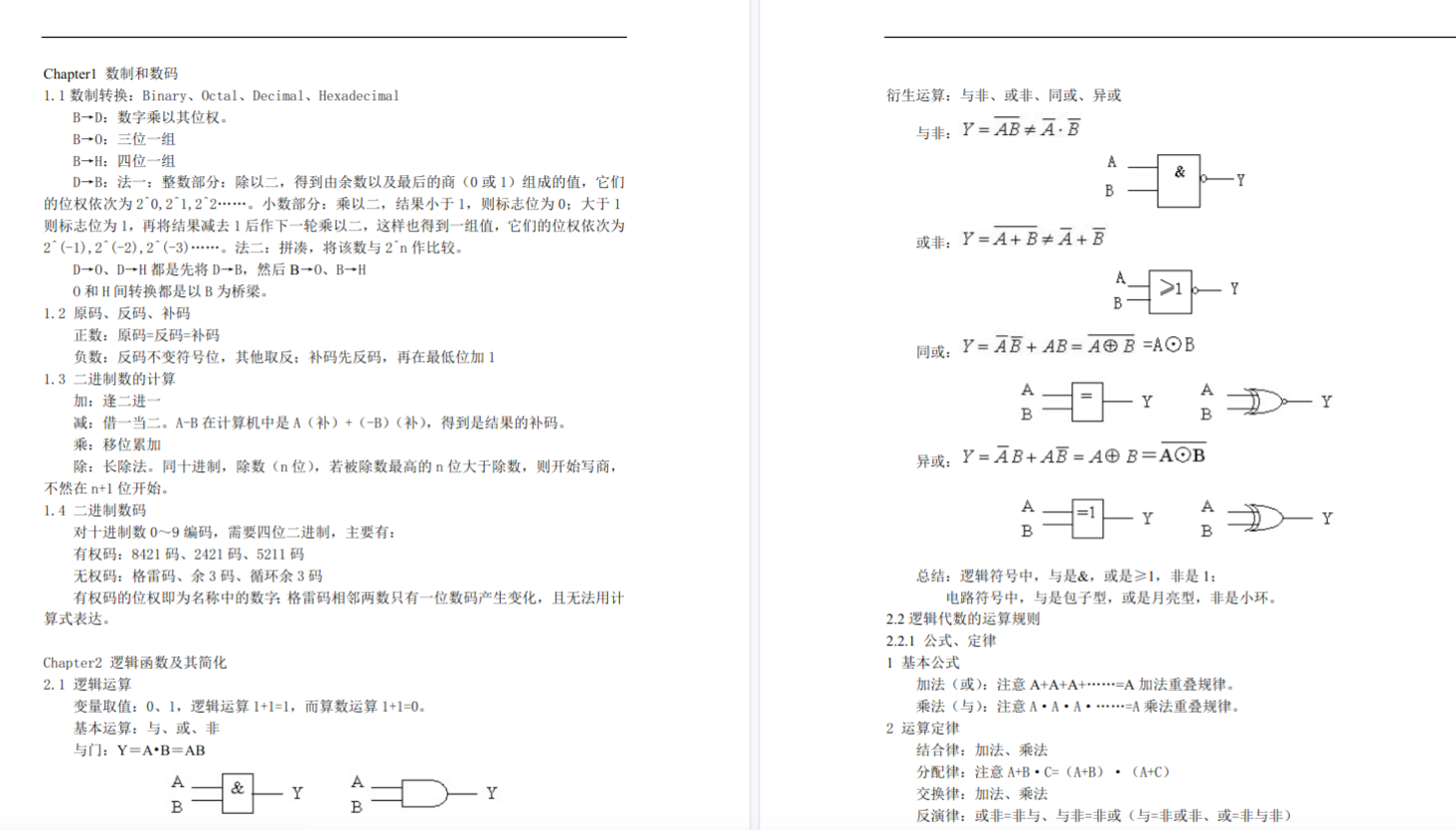

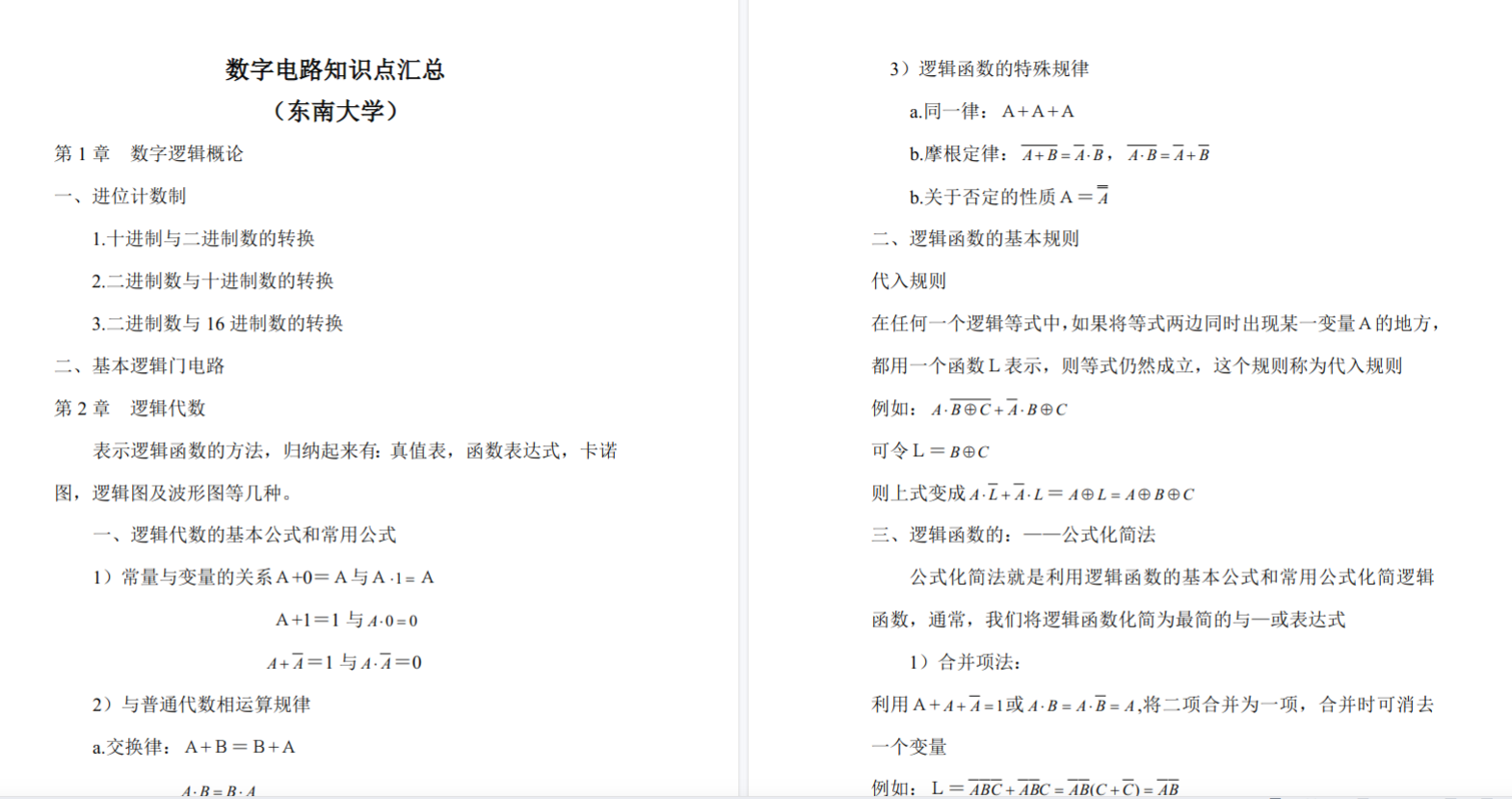

第一,以“逻辑代数”为地基,以“组合与时序”为两大支柱重构知识体系。 数字电路的知识体系非常清晰。地基是逻辑代数(数制转换、布尔代数、卡诺图化简),这是所有分析和设计的工具。在此基础上,分出两大支柱:

-

组合逻辑电路:输出只取决于当前输入(如加法器、译码器、数据选择器)。核心是“逻辑表达式 → 电路图”的相互转换,以及利用MSI(中规模集成电路)实现复杂功能 。

-

时序逻辑电路:输出不仅取决于当前输入,还取决于过去的输入(由触发器构成)。核心是状态转换,你必须熟练掌握触发器(JK、D、T)的特性方程,以及同步/异步计数器的分析和设计。

第二,死磕“卡诺图化简”和“时序电路分析”这两大理论心脏。 这是拉开分数的关键,也是计算题的必考点:

-

卡诺图化简:这是组合逻辑设计的基本功。要能快速、准确地用卡诺图化简逻辑函数,特别是包含无关项的化简。这直接决定了后续电路设计的成本和可靠性。

-

时序电路分析:包括根据电路图画出波形图、写出状态转换表/图、判断计数器模长。特别是同步时序逻辑电路的设计(给定功能要求,设计出状态图、状态表、驱动方程、输出方程),是区分“懂”和“精通”的分水岭。

第三,建立“MSI芯片”的功能库。 考试中常让你用常用的中规模集成电路(如74LS138译码器、74LS151数据选择器、74LS161计数器)来实现任意逻辑功能。复习时要总结这些芯片的功能表和控制引脚,把它们当作你的“硬件函数库”来记忆。

第四,重视“555定时器”和“A/D、D/A”的工程应用。 555定时器可以构成施密特触发器、单稳态触发器、多谐振荡器,是脉冲波形产生和整形电路的核心,必须搞懂其内部结构和工作原理。A/D和D/A转换器则要掌握权电阻网络、倒T型网络的工作原理,以及转换精度、转换速度等关键指标。

第五,答题时呈现“数字设计师”的严谨。 做题时,特别是设计题,要遵循规范的步骤(如“逻辑抽象 → 真值表 → 逻辑表达式 → 化简 → 逻辑图”)。让阅卷人看见你清晰的逻辑推导过程,而不是最终答案。