资料目录(截图原因可能偏模糊,实际都是高清版)

备考唐朔飞《计算机组成原理》,你需要深刻理解这本经典教材的体系化精髓:它系统构建了从“数字逻辑基础”到“完整CPU设计”的严谨硬件世界观,核心在于掌握“数据表示→运算方法→CPU数据通路与控制器设计→存储与I/O系统”的逐层构建逻辑。 备考关键在于 “建立清晰的层次化硬件抽象认知,精通核心部件的互连与协同工作原理,并能通过数据通路与微操作序列,透彻分析指令执行的完整时空过程”。以下是为你设计的针对性备考策略。

高效备考四步法:

第一步:构建“基础-核心-系统”三层知识框架,紧扣教材主线

紧扣唐版教材的经典结构,建立稳固的知识体系:

-

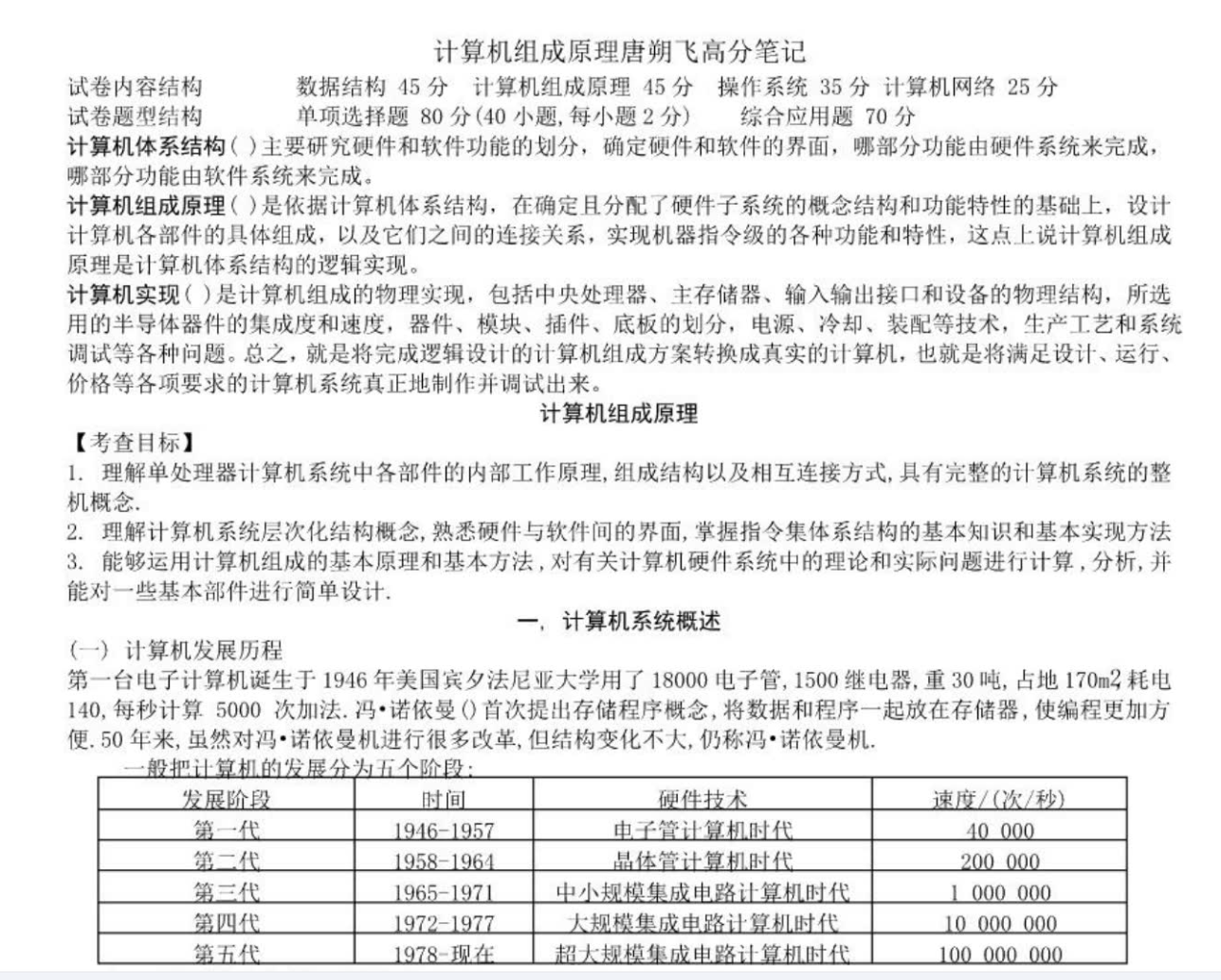

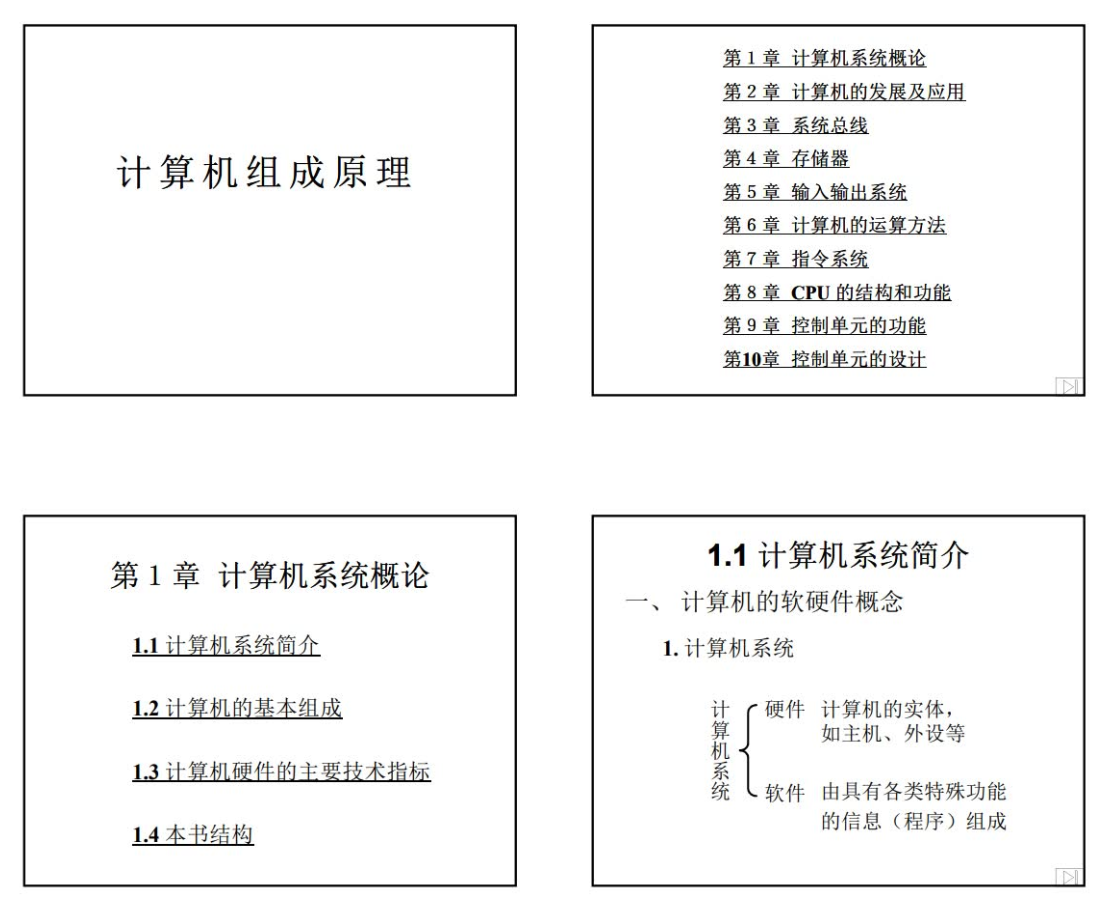

计算机系统概论与数据表示:理解计算机系统的层次结构,并务必攻克运算方法(定点、浮点加减乘除)的详细算法流程与电路实现思想,这是后续理解运算器与控制器的关键前置知识。

-

中央处理器(CPU)的设计核心:这是全书的灵魂与绝对重点。必须彻底吃透 CPU的功能和组成、指令系统(寻址方式、指令格式)、运算器的结构(ALU、寄存器)、控制器的设计原理(微程序控制器、硬布线控制器)。重中之重是 数据通路 的构建与 指令执行过程 的微操作序列分析。

-

存储系统与输入输出系统:掌握 存储器的层次结构(Cache-主存-辅存),重点是 Cache的多种映射方式与替换算法,以及 虚拟存储器的页式管理。理解 I/O方式(程序查询、中断、DMA) 的原理与过程,尤其是 中断的完整处理流程。

第二步:聚焦“CPU数据通路与指令执行”和“存储系统映射机制”两大堡垒

这是唐版教材深度与考试计算、分析、设计题的绝对重心。

-

CPU数据通路与微操作序列分析:必须能绘制并解释简化的 单总线或多总线CPU数据通路图。面对一条具体指令(如ADD, LOAD, STORE, JMP),能够 按周期(取指、间址、执行、中断)清晰阐述其完整的执行流程,并准确说明每一个节拍(时钟周期)内 各功能部件的控制信号状态和数据流动方向。这是衡量你是否“学懂”的最高标准。

-

存储系统的性能分析与地址映射:熟练完成 Cache命中率、平均访问时间 的计算。必须能透彻分析在 直接映射、全相联、组相联 下,主存地址到Cache地址的 映射、定位与替换过程。同时掌握在页式虚拟存储中,逻辑地址到物理地址的转换过程(通过页表,可能涉及TLB)。

第三步:采用“绘图推演与流程精析”深度学习法

针对唐版教材理论性强、逻辑严密的特点,必须将抽象设计具象化。

-

“亲自动手,绘制与推演”:合上教材,亲手绘制 ALU与寄存器组的简化连接图、单周期CPU数据通路总图、微程序控制器组成原理图、Cache与主存的映射关系示意图。在通路图上,选择典型指令,一步步推演其执行,并同步写出每一步所需的 微操作命令(控制信号)。

-

“对比辨析,深化理解”:制作对比表格,清晰比较 微程序控制器与硬布线控制器 在 原理、组成、性能、灵活性 上的根本区别;比较 程序查询、中断、DMA 三种I/O方式的特点与应用场景。

-

“以题带点,攻克运算”:对唐版教材中详细的 定点/浮点四则运算 例题与习题,必须动手演算,理解其算法步骤与可能出现的溢出等异常情况处理。

第四步:冲刺阶段:真题驱动与综合贯通

-

精研教材习题与真题:唐版教材的课后习题极具代表性,务必全部弄懂。分析历年真题,明确考试是侧重概念、计算、指令流程分析,还是简单的控制器设计思想阐述。

-

专题深度整合:

-

专题一:CPU数据通路与指令执行全流程分析。

-

专题二:存储器层次结构(Cache+虚存)综合性能计算与地址映射。

-

专题三:I/O系统与中断处理全过程。

-

若资料存在问题或网盘链接失效,请联系本站客服QQ2484803760,每天工作时间:上午8点—晚上10点

声明:本站所有文章,如无特殊说明或标注,均为本站原创发布。任何个人或组织,在未征得本站同意时,禁止复制、盗用、采集、发布本站内容到任何网站、书籍等各类媒体平台。如若本站内容侵犯了原著者的合法权益,可联系我们进行处理。