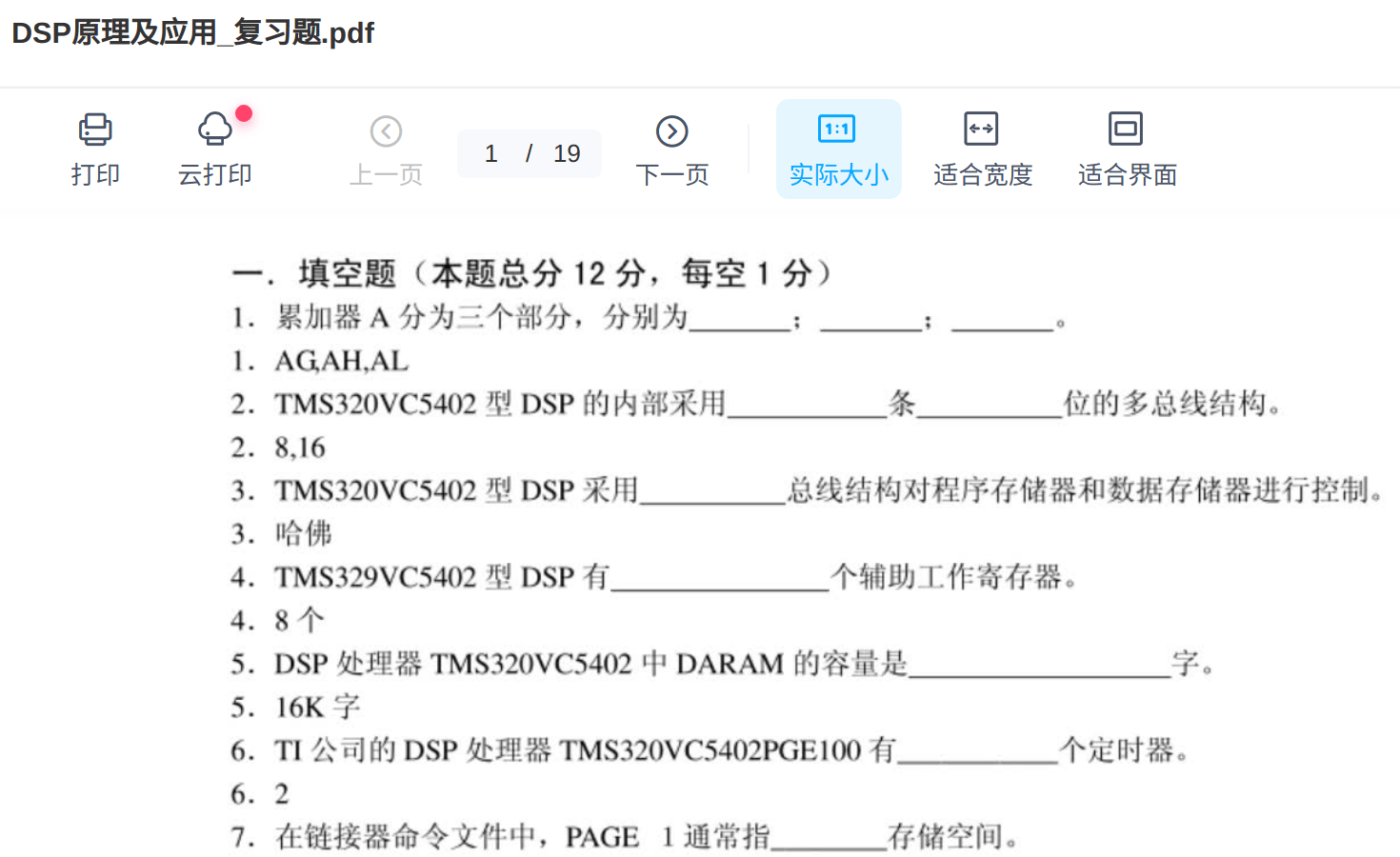

资料目录(截图原因可能偏模糊,实际都是高清版)

《DSP原理与应用》高效备考策略

一、课程特征与备考逻辑

本课程是“理论算法+芯片架构+实践编程”的三维融合,备考需突破三大难点:

-

理论抽象性:离散信号变换、滤波器设计等数学推导

-

体系独特性:哈佛架构、硬件乘法器、循环寻址等专用结构

-

实践综合性:需将算法流程转化为可执行的芯片指令

命题规律通常呈“433”分布:40%基础概念+30%原理分析与计算+30%系统设计与编程。

二、三阶段备考攻坚路径

第一阶段:双链搭建与核心突破(15天)

-

建立两条主线:

-

算法链:连续信号采样→离散序列→Z变换→DFT/FFT→数字滤波器设计

-

硬件链:TI TMS320系列架构→总线结构→专用寄存器→指令系统→外设接口

-

-

手绘关键框图:

-

FFT蝶形运算流程(重点8点FFT)

-

FIR/IIR滤波器结构图(直接型/级联型)

-

DSP芯片数据流(从ADC到DAC的完整路径)

-

第二阶段:专题精讲与计算训练(20天)

-

FFT专题:

-

掌握时间抽取法计算流程

-

完成4点、8点FFT手工演算(每年必考)

-

理解FFT减少运算量的本质(NlogN与N²对比)

-

-

滤波器设计专题:

-

窗函数法设计FIR:明确矩形窗、汉宁窗、汉明窗的性能差异

-

双线性变换法设计IIR:掌握预畸变补偿计算

-

完成一个“给定指标→选择方法→计算阶数→确定系数”的完整设计题

-

-

芯片体系专题:

-

整理核心资源表:

乘法器:单周期完成16×16位乘法 循环缓冲区:实现FIR滤波的关键 零开销循环:提升算法效率的硬件支持

-

汇编/C语言混合编程要点:中断服务程序的编写框架

-

第三阶段:系统设计与真题实战(15天)

-

设计题标准化流程:

问题分析 → 算法选择 → 资源分配 → 流程设计 → 代码框架

-

经典题型突破:

-

语音信号处理系统:采样率确定→抗混叠滤波→FFT分析→滤波处理

-

数字控制系统:ADC量化误差分析→数字PID实现→输出 PWM 生成

-

-

真题演练重点:

-

选择题:关注“唯一性”描述(如“只有DSP具备…”)

-

计算题:规范书写步骤,尤其是中间变量符号说明

-

编程题:注释需体现“算法思想与硬件资源对应关系”

-

三、关键提分技巧

-

概念辨析法:

-

DFT vs. FFT(计算量对比)

-

FIR vs. IIR(结构、稳定性、相位特性)

-

哈佛架构 vs. 冯·诺依曼架构(并行性差异)

-

-

计算题规范:

-

FFT计算采用“蝶形图分步法”,每步标注旋转因子

-

滤波器设计题保留6位小数,明确写出单位脉冲响应h(n)或系统函数H(z)

-

-

编程题框架:

// 典型FIR滤波器实现框架(重点展示硬件特性利用) #include “register.h” // 映射硬件寄存器 int yn = 0; // 输出初始化 #pragma CODE_SECTION(fir_filter, ”.text:fir”) // 指定程序段 void fir_filter(int xn) { static int buffer[N]; // 循环缓冲区 // 1. 更新缓冲区(利用循环寻址) // 2. 乘累加计算(利用硬件乘法器与MAC指令) // 3. 返回结果 }

四、资源整合方案

-

理论核心:程佩青《数字信号处理教程》重点章节

-

芯片手册:精读TI TMS320C54x或C6000系列数据手册的关键章节

-

实验指导:完成至少3个完整实验(如:音频滤波、频谱分析)

五、时间规划建议

-

晨间(30分钟):记忆核心概念对、芯片关键参数

-

日间(90分钟):专题精解与计算训练

-

晚间(60分钟):程序阅读或设计,绘制系统框图

-

周末(3小时):完成一套完整模拟题,重点突破设计大题

备考的本质是将抽象的离散数学理论与具体的芯片操作相结合。建议制作“理论公式-物理意义-硬件实现”三位一体的知识卡片,最终达到“给定一个应用场景,能快速映射到算法流程并预估所需芯片资源”的应试能力。

(注:不同院校侧重芯片型号不同,请根据实际教学使用的DSP型号调整芯片架构细节。)