资料目录(截图原因可能偏模糊,实际都是高清版)

备考《数字电子技术》,最致命的误区是把它当成“模拟电路”的延伸或孤立地死记真值表。这门课的本质是研究数字信号的逻辑处理与电路实现,核心是“逻辑”而非“电平”。

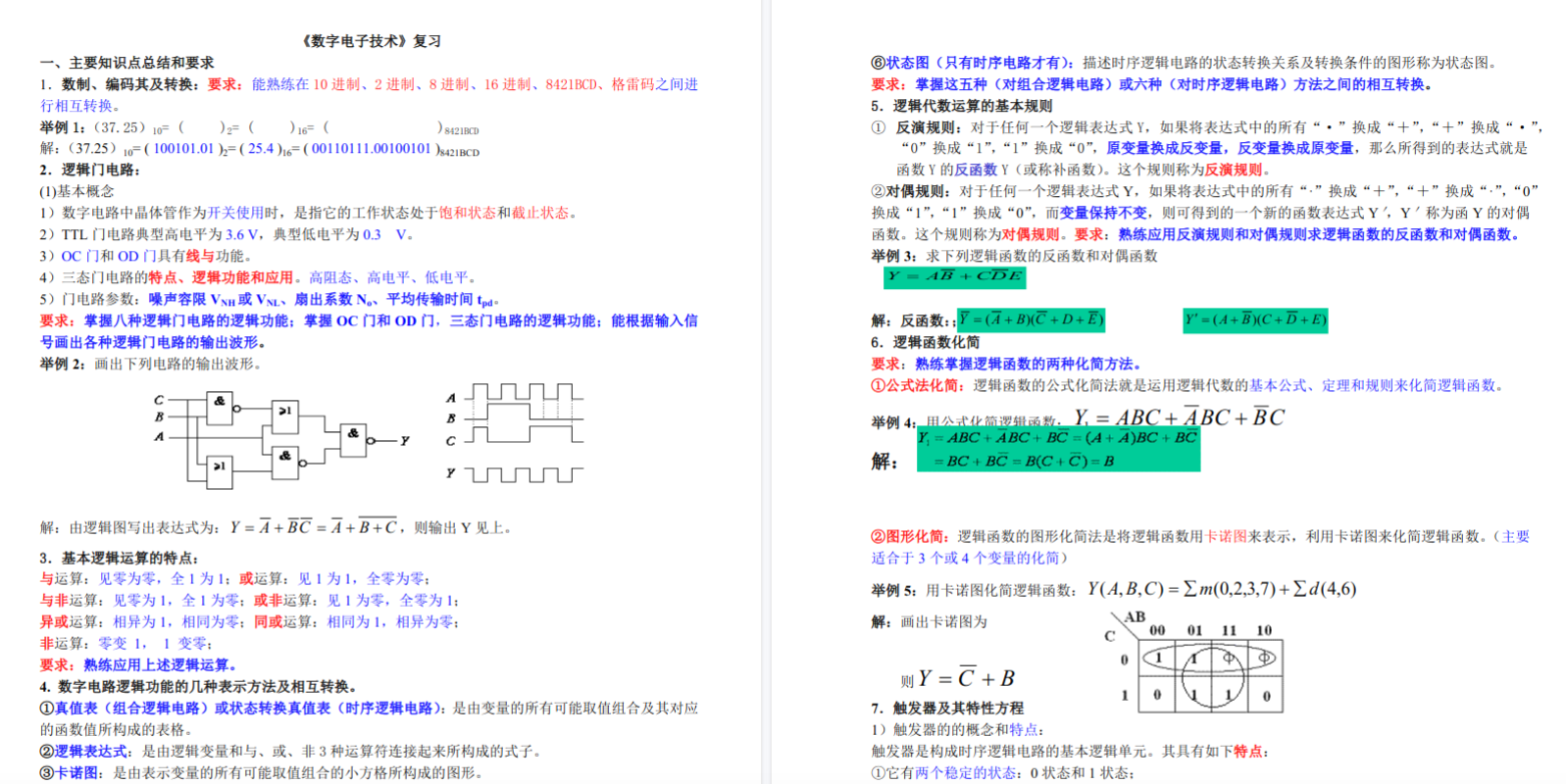

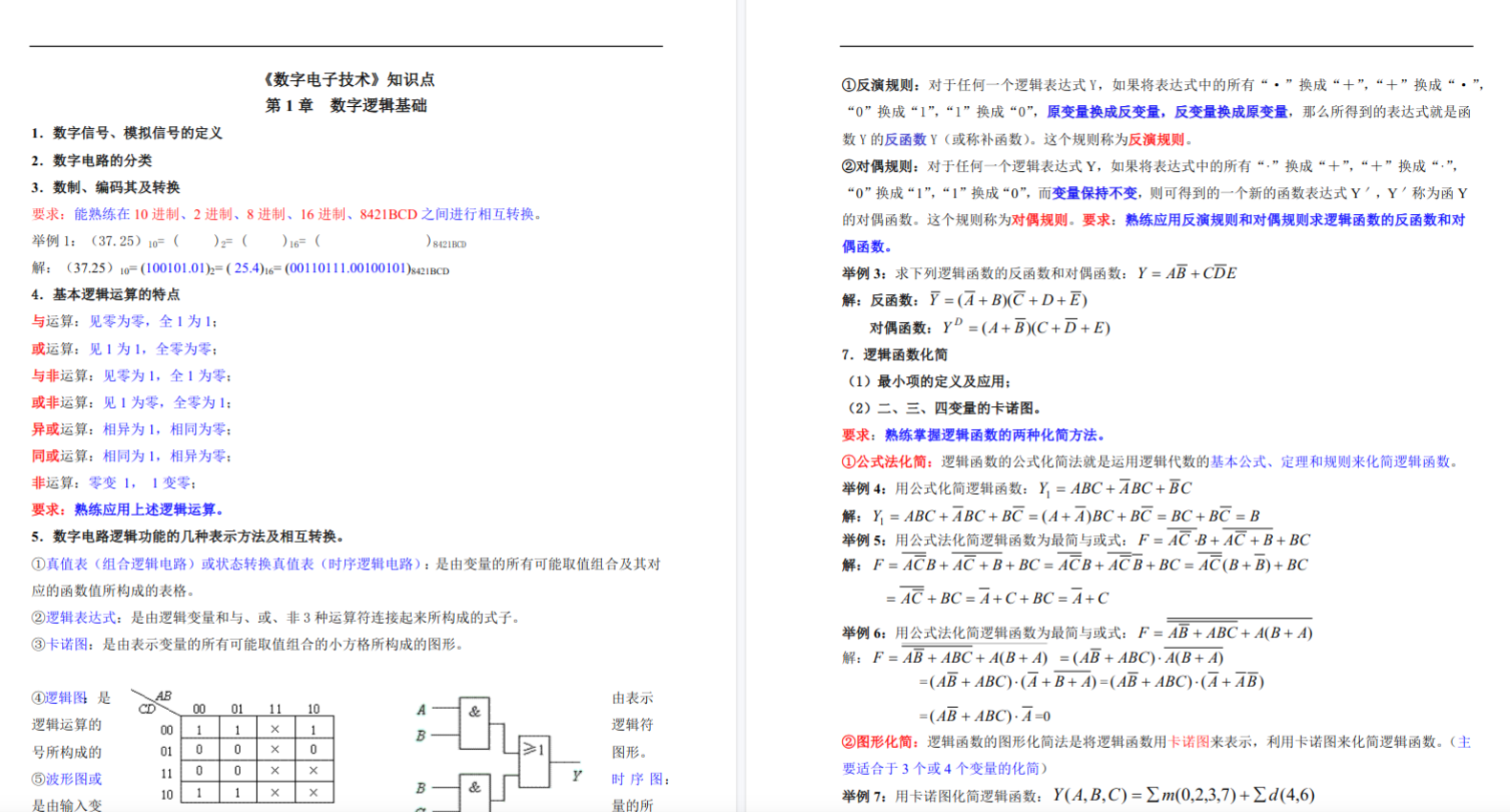

第一,以“逻辑代数”为地基,以“组合与时序”为两大支柱重构知识体系。 地基是数制转换、卡诺图化简,这是所有分析和设计的工具。在此基础上,组合逻辑(如译码器、数据选择器)的核心是表达式与电路图的互转;时序逻辑的核心是状态转换,必须吃透触发器特性方程和计数器设计。

第二,死磕“化简能力”和“时序分析”这两大理论心脏。 这是拉开分数的关键。卡诺图化简(特别是包含无关项)决定了设计的成本;时序逻辑中,根据电路图画出波形图、写出状态转换表,以及同步时序电路的设计(从功能到状态图、驱动方程),是区分“懂”和“精通”的分水岭。

第三,答题时呈现“数字设计师”的严谨。 设计题要遵循“逻辑抽象→真值表→表达式→逻辑图”的规范步骤。推荐资源:阎石《数字电子技术基础》搭配刘家琪《考研专业课真题必练》,通过大量实战掌握设计题的灵活套路。

若资料存在问题或网盘链接失效,请联系本站客服QQ2484803760,每天工作时间:上午8点—晚上10点

声明:本站所有文章,如无特殊说明或标注,均为本站原创发布。任何个人或组织,在未征得本站同意时,禁止复制、盗用、采集、发布本站内容到任何网站、书籍等各类媒体平台。如若本站内容侵犯了原著者的合法权益,可联系我们进行处理。